|

IoT機器等の組込み計算機システムの性能は、データを処理する算術演算回路のハードウェアアルゴリズム(算術ハードウェアアルゴリズム)に大きく左右される。近年では、従来の2 進数だけでなく、用途に応じて多様な数系に基づく算術が必要とされている。特に、個人情報保護や高信頼な電子商取引を実現する処理(暗号処理や誤り訂正処理)を行うシステムの応用が近年急速に拡大しており、その処理に必須となるガロア体上の算術ハードウェアアルゴリズムの重要性はますます高まっている。

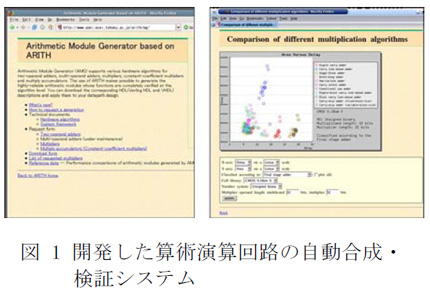

受賞者は、上記のように複雑化する計算機システムの設計問題を解決する新しい設計パラダイムとして、算術ハードウェアアルゴリズムの高水準な設計・検証・合成技術を開発してきた。特に、2進数と非2進数を統合した算術式に基づく算術ハードウェアアルゴリズムの設計手法を発案し、それに基づく算術演算回路の合成・検証システムを世界に先駆けて開発した。同システムは、多様な算術演算回路を、その機能を完全に保証した上で高速に合成できる。これは、高度な計算機代数の技法を応用した形式的回路検証手法によって初めて実現されたものである。現在、同システムは、従来困難とされた1000種類を越える算術演算回路の合成を実現しており、インターネットを通して世界中から利用されている(図1)。

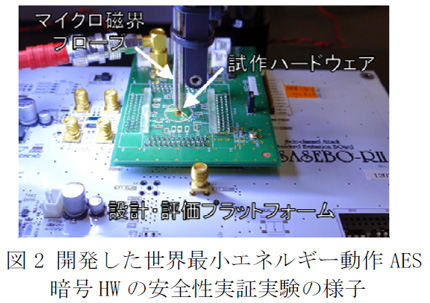

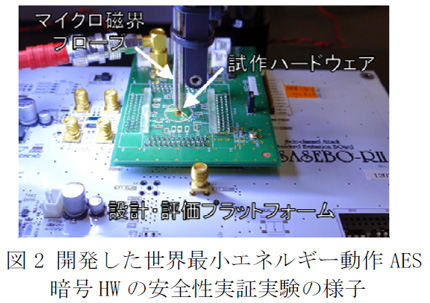

また、受賞者の開発した技術は、算術ハードウェアアルゴリズムのレベルから高い安全性を実現する新しい情報セキュリティ(ハードウェアセキュリティ)分野にも発展している。一例として、国際標準暗号AES(Advanced Encryption Standard)への応用では、世界最小エネルギー動作可能な耐タンパー性AES暗号ハードウェアの設計と完全な検証に成功している(図2)。また、開発した暗号処理ハードウェア全般に有効な実装安全性解析手法は、ISO/IEC国際標準規格に参照されるなど、学術的・社会的に高く評価されている。さらに、受賞者らが開発したセキュリティハードウェアの設計・評価用プラットフォームは、国内外の多数の企業・大学・研究機関で採用されており、事実上の世界標準となっている。

|